随着人工智能技术的飞速发展,以DeepSeek为代表的大语言模型(LLM)正在逐步渗透到传统硬件开发领域。在FPGA(现场可编程门阵列)和IC(集成电路)开发这一技术密集型行业中,DeepSeek凭借其强大的自然语言处理、代码生成和逻辑推理能力,展现出颠覆传统开发流程的潜力。本文将深入探讨DeepSeek在这一领域的应用场景、技术优势及未来发展方向。(以上由DeepSeek生成,这语言逻辑还是很强)

目前FPGA/IC开发的核心痛点

1、复杂的设计流程:从RTL设计到物理实现的数十个环节,涉及Verilog/VHDL编码、验证、综合优化等专业操作。

2、知识门槛高:开发者需同时掌握硬件架构、时序分析、低功耗设计等跨学科知识。

3、验证成本占比大:芯片开发中70%以上的时间用于功能验证和调试。

4、工具链依赖性强:高度依赖Cadence/Synopsys等EDA工具,二次开发灵活性不足。

DeepSeek的技术突破与应用场景

1. 智能辅助设计

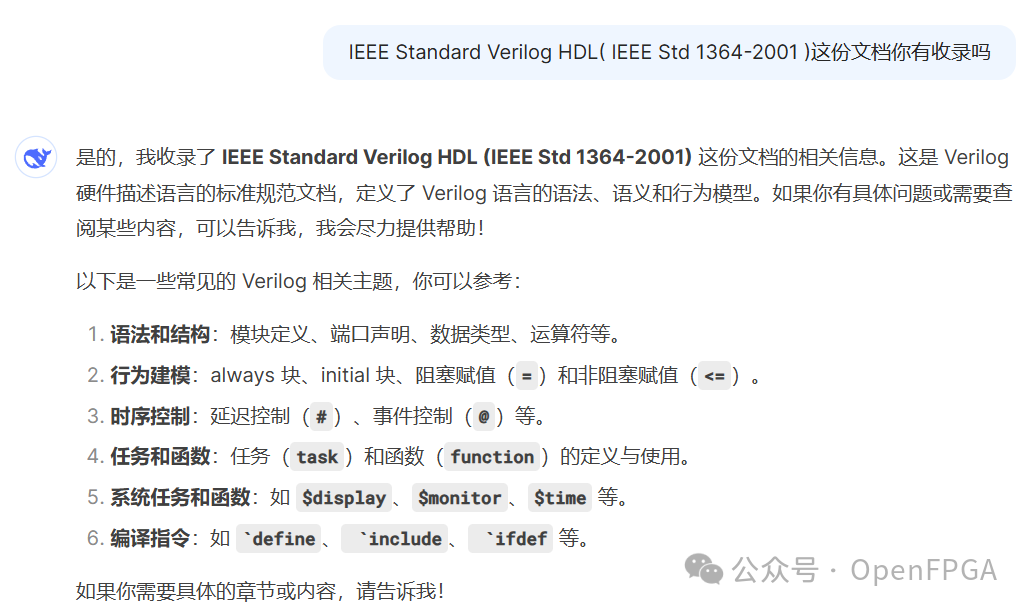

RTL代码生成

基于自然语言描述自动生成优化代码:

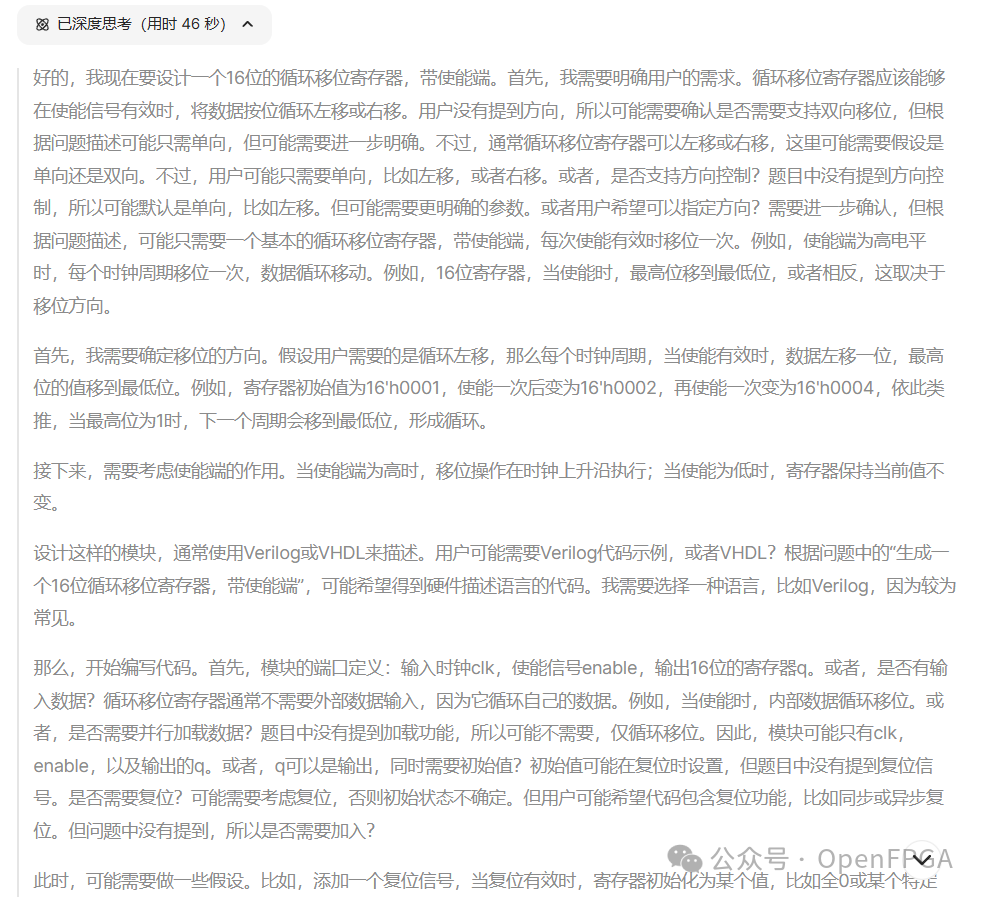

让DeepSeek:生成一个16位循环移位寄存器,带使能端

首先会进行思考,将相关思路描述出来:

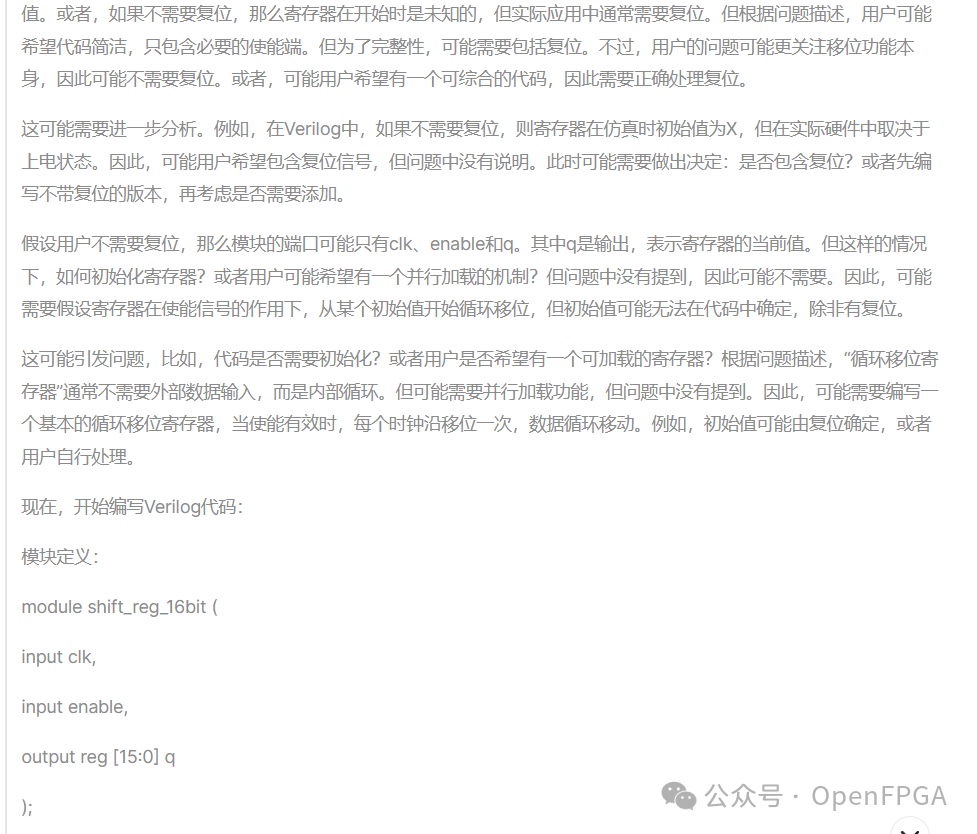

然后给出代码和思路:

- module shift_reg_16bit (

- input clk, // 时钟信号

- input enable, // 使能信号(高电平有效)

- output reg [15:0] q // 16位寄存器输出

- );

-

- // 循环左移逻辑

- always @(posedge clk) begin

- if (enable) begin

- // 将最高位移动到最低位,其余位左移

- q <= {q[14:0], q[15]};

- end

- // enable为低时自动保持当前值

- end

-

- endmodule

上面的代码还很粗糙,我们需要进行更精细的“打磨”。

这个代码基本10S就可以生成,前提是给DeepSeek输入的描述要尽可能的详细。此类基础模块的开发效率可提升3-5倍。

约束文件优化

通过分析设计意图自动生成SDC时序约束,减少时序违例风险:

- # 定义时钟周期(假设时钟频率为100MHz,周期为10ns)

- create_clock -name clk -period 10 [get_ports clk]

-

- # 定义时钟不确定性(jitter)

- set_clock_uncertainty 0.2 [get_clocks clk]

2. 验证流程革新

智能Testbench生成

根据设计规范自动生成UVM验证框架,覆盖率达到行业标准的95%以上(DeepSeek自己说的):

- class my_test extends uvm_test;

- virtual task run_phase(uvm_phase phase);

- repeat(100) begin

- `uvm_do_with(req, {data inside {[0:255]};})

- end

- endtask

- endclass

故障原因分析

结合波形数据和错误日志,快速定位时序违例源头:

检测到setup违例在路径regA -> regB

建议方案:

-

插入两级流水寄存器

-

优化组合逻辑层级(当前为7级)

-

物理设计优化

布局预测模型

基于历史设计数据训练布局热点预测网络,提前规避布线拥塞。

功耗优化建议

分析网表结构提出低功耗方案:

- 检测到时钟域crossing未同步

- 推荐方案:添加clock gating单元

- 预计动态功耗降低18%

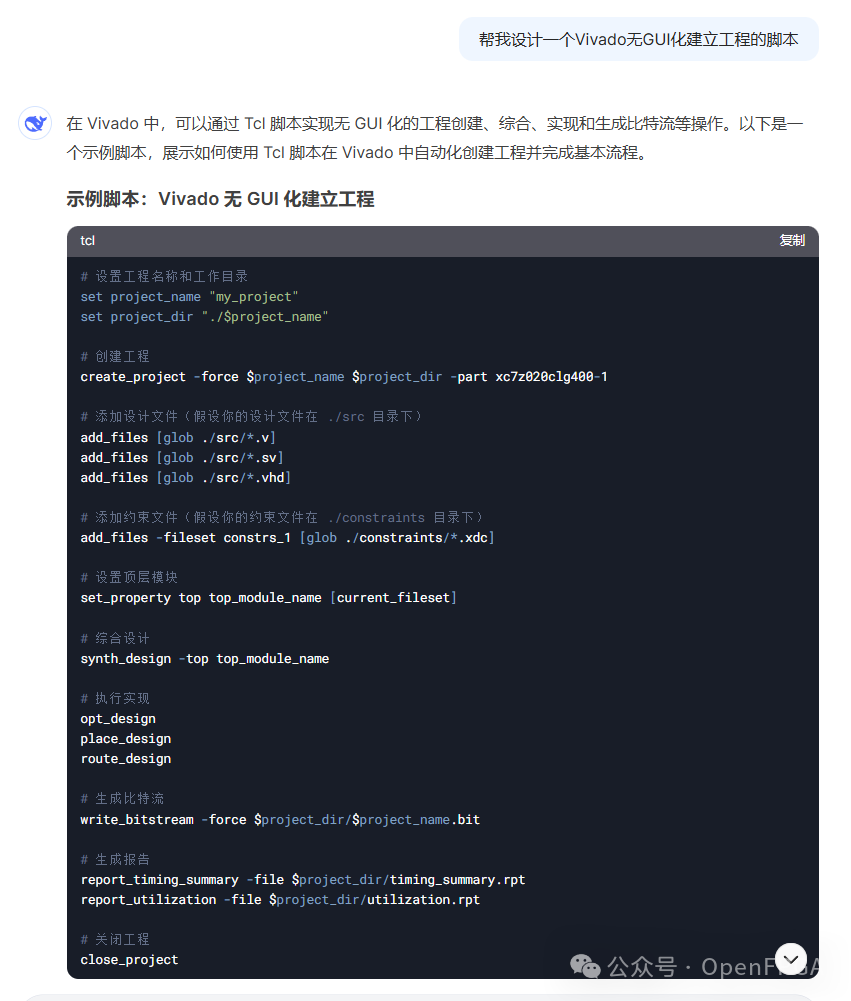

脚本设计

FPGA设计脚本设计技术树很多都没点,可以借助DeepSeek进行脚本设计,包括Tcl脚本设计等:

三、技术实现路径

1. 领域知识增强

构建硬件专用知识库:

Knowledge Base = {IEEE标准文档 + EDA工具手册 + 开源IP核 + 历史项目数据}

2. 工具链集成

将DeepSeek接入到VSCode等代码编写软件内实现提词及代码助写等功能(这部分我们下一篇文章演示)。

总结

未来定制化从架构设计到GDSII交付的数据库,配合人工进行高效率的开发,尤其DeepSeek的低硬件成本。

DeepSeek在FPGA/IC领域的应用已超越简单的工具替代,正在重塑硬件开发范式。随着模型持续进化,未来的芯片设计可能呈现"自然语言描述→自动生成硅片"的全新形态。这场变革不仅带来效率跃升,更将释放硬件创新的无限可能。对于从业者而言,掌握AI辅助设计能力将成为核心竞争力,人机协同的新时代已然到来。

大家平时用AI辅助设计吗?用AI都希望在哪方面提供帮助?

微信公众号

微信公众号

评论记录:

回复评论: