苦难从不值得歌颂,在苦难中萃取的坚韧才值得珍视;

痛苦同样不必美化,从痛苦中开掘出希望才是壮举。

没有人是绝对意义的主角,

但每个人又都是自己生活剧本里的英雄。

滑雪,是姿态优雅的“贴地飞行”,也有着成长的隐喻。

高低错落的雪道里,滑雪者不断出发,

挑战自我,追求卓越,向往自由,

滑雪运动的魅力尽显。

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

XC7A100T-2FGG484I是赛灵思(Xilinx)公司Artix-7系列FPGA的一款产品。以下是关于该型号的主要信息和应用领域:

主要信息

- 属于Artix-7系列FPGA,工艺制程为28nm

- 封装为484引脚BGA封装

- 逻辑资源包括101,440个逻辑单元、240个DSP切片、4.86Mb块RAM

- 支持DDR3/DDR3L/LPDDR2/DDR2存储器控制器

- 支持高速串行收发器,最高传输速率12.5Gbps

- 支持PCI Express Gen2控制器

主要应用领域

- 通信设备

- 工业控制

- 视频处理

- 数据中心加速器

- 无线基站

- 手机基带处理

XC7A100T-2FGG484I作为中低端Artix-7系列FPGA,具有较高的性能和较低的功耗,非常适合通信、工业控制、视频处理等领域的应用。同时也可用于数据中心加速器和无线基站等领域 。

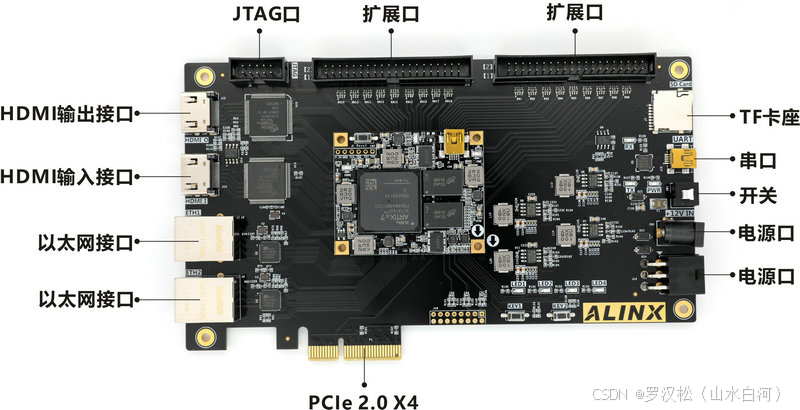

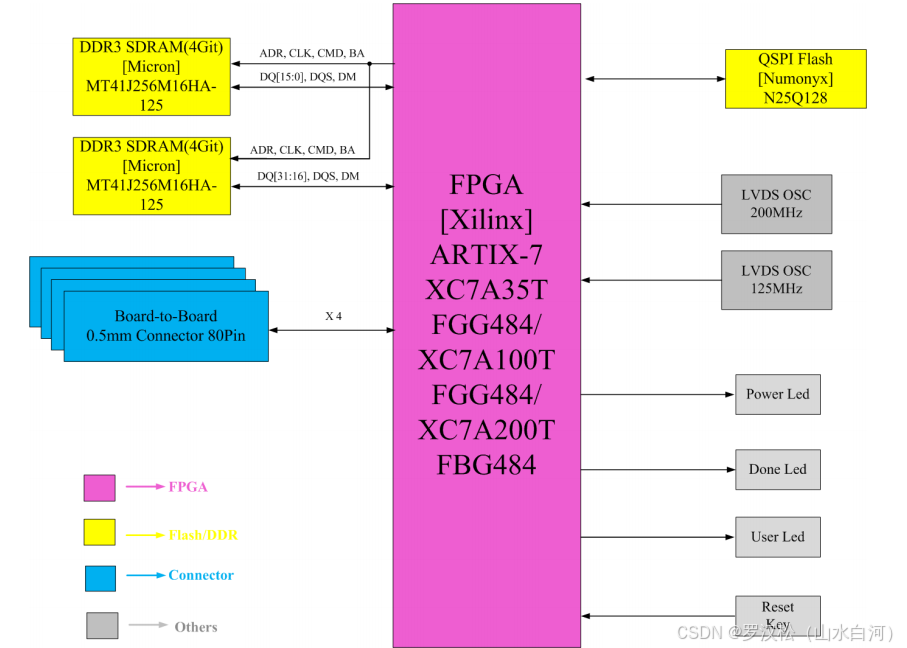

XC7A100T-2FGG484I核心板使用了2片MICRON公司的MT41J256M16HA-125 DDR3芯片,组合成32bit的数据总线宽度。1个128Mb的QSPI FLASH用来静态存储FPGA芯片的配置文件或者其它用户数据。底板为核心板扩展了丰富的外围接口,其中包含PCIe、千兆以太网、HDMI输入输出接口等等。

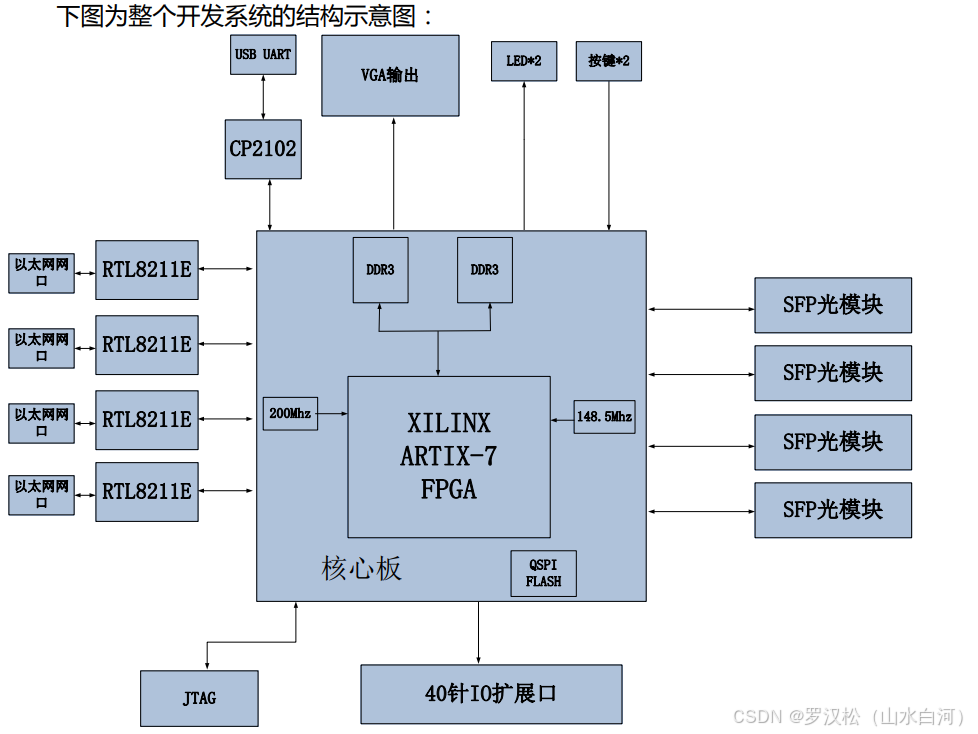

通过这个示意图,我们可以看到,我们这个开发平台所能实现的功能。

- Artix-7 FPGA 核心板

由 XC7A100T+8Gb DDR3+128Mb QSPI FLASH组成,另外有两个高精度 Sitime公司的 LVDS 差分晶振,一个是 200MHz,另一个是 125MHz,FPGA 系统和 GTP模块提供稳定的时钟输入。 - 四路 10/100M/1000M 以太网 RJ-45 接口千兆以太网接口芯片采用 Realtek 公司的 RTL8211EG 以太网 PHY 芯片为用户提供网络通信服.RTL8211EG 芯片支持 10/100/1000 Mbps 网络传输速率; 全双工和自适应。

- 四路 SFP 高速光纤接口

ARTIX-7 FPGA 的 GTP 收发器的 4 路高速收发器连接到 4 个光模块的发送和接收,实现 4 路高速的光纤通信接口。每路的光纤数据通信接收和发送的速度高达 6.6Gb/s。 - 一路 VGA 输出

16 位色的 VGA 模拟输出, RGB565 格式,可以产生 32 个梯度等级的红色和蓝色信号和 64 个梯度等级的绿色信号; - 一路 USB Uart 调试接口

一路Uart转USB接口,用于和电脑通信,方便用户调试。串口芯片采用Silicon Labs CP2102GM 的 USB-UAR 芯片, USB 接口采用 MINI USB 接口。 - 40 针扩展口

预留 1 个 40 针 2.54mm 间距的扩展口,可以外接黑金的各种模块(双目摄像头,TFT LCD 屏,高速 AD 模块等等)。扩展口包含 5V 电源 1 路,3.3V 电源 2 路,地 3 路,IO 口 34 路。 - JTAG 口

10 针 2.54mm 标准的 JTAG 口,用于 FPGA 程序的下载和调试; - 按键

2 按键,1 个复位按键(在核心板); - LED 灯

3 个用户发光二级管 LED(1 个在核心板,2 个在扩展板)

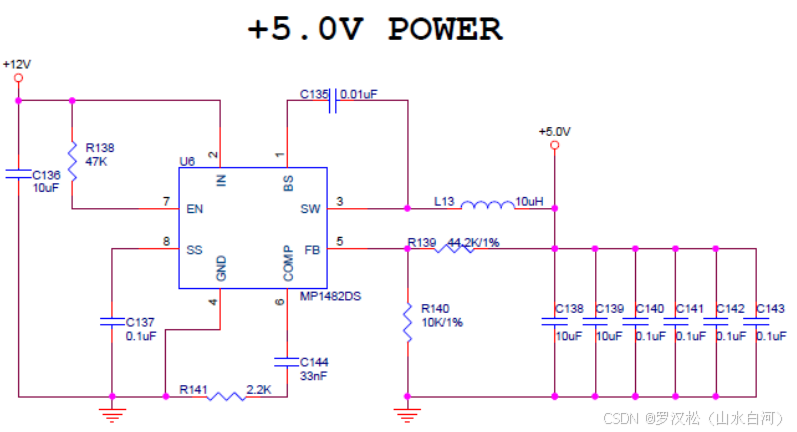

供电电源

开发板的电源输入电压为 DC12V,请使用开发板自带的电源,不要用其他规格的电

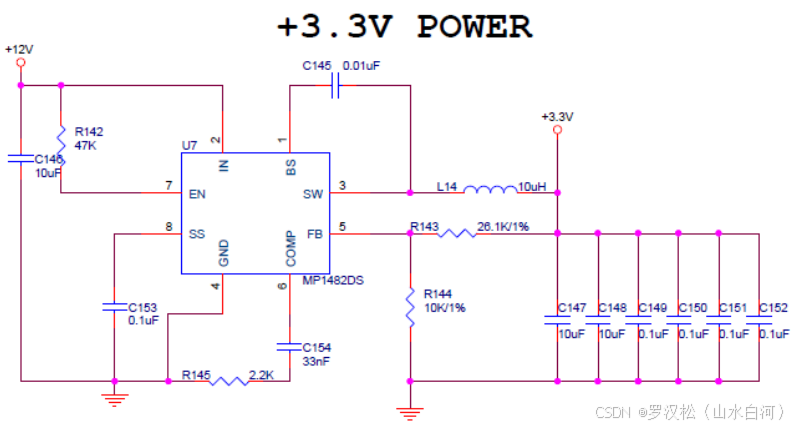

源,以免损坏开发板。扩展板上通过2路DC/DC电源芯片MP1482转化成+5V和+3.3V

两路电源。另外扩展板上的+5V 电源通过板间连接器给核心板供电,扩展上的电源设计

如下图 3-10-1 所示

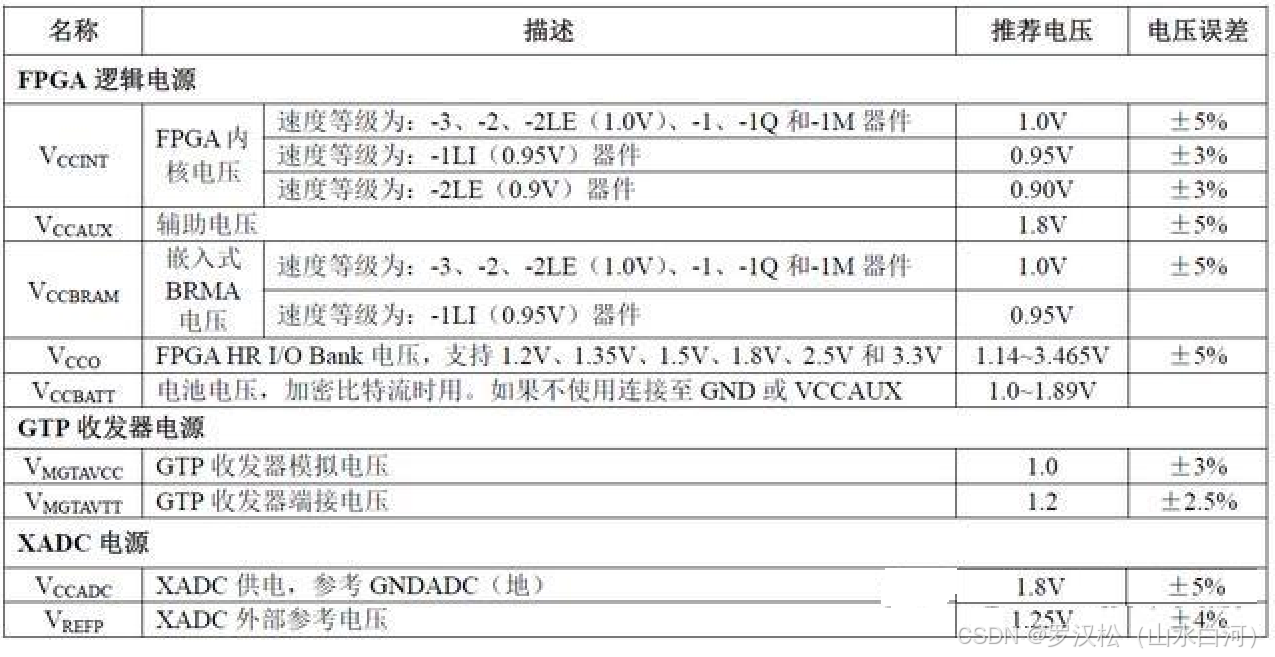

Artix-7 FPGA芯片提供三种类型电源:FPGA逻辑资源电源、GTP收发器电源和XADC电源。每种电源的设计要求如图1所示。FPGA I/O按照Bank进行划分,以增强I/O设计的灵活性,图1中所示的VCCO每种电压允许误差均为±5%。

评论记录:

回复评论: